### Si TECHNOLOGY ROADMAP FOR UBIQUITOUS COMPUTING, SENSING, AND PERCEPTION

## Dr Dennis Buss Texas Instruments Inc buss@ti.com

## Si TECHNOLOGY ROADMAP FOR UBIQUITOUS COMPUTING AGENDA

- ► Moore's Law Scaling

- Design for Low Power

- SOC Integration of Analog/RF Functions

- Digital Radio Processor

- Integrated MEMS

- Conclusion

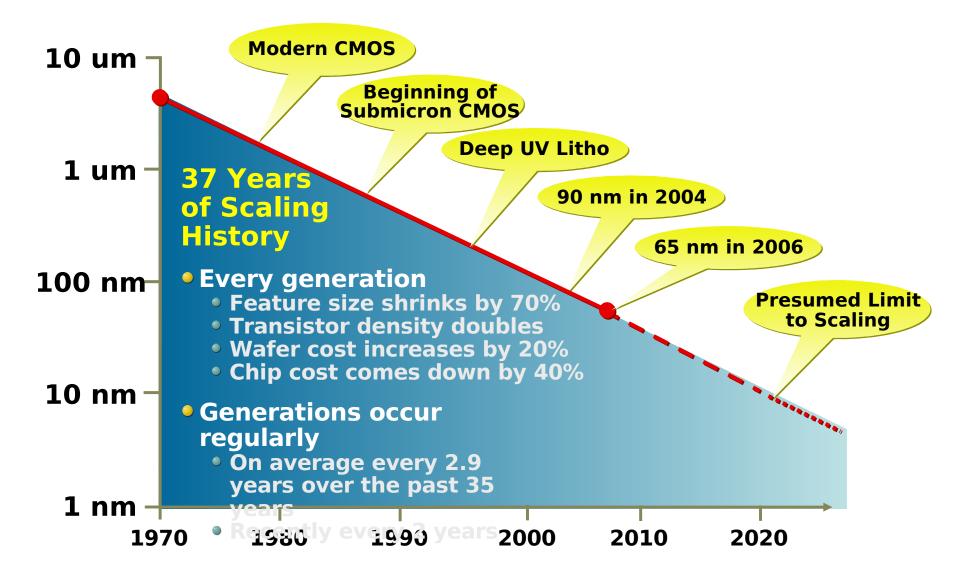

### Semi-Conductor Scaling

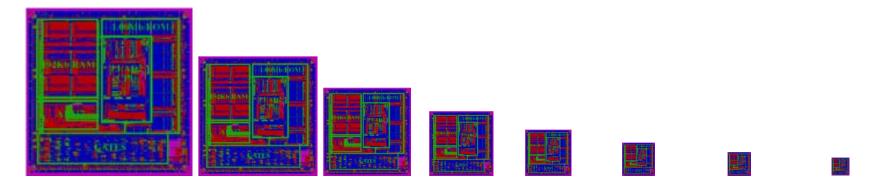

### **GSM Digital Baseband Evolution**

| Year              | 1994  | 1997                   | 1999  | 2000  | 2002   | 2004   | 2006       | 2008       |

|-------------------|-------|------------------------|-------|-------|--------|--------|------------|------------|

| Nano-<br>meter    | 500nm | 350n                   | 250nm | 180nm | 130nm  | 90nm   | 65nm       | 45nm       |

| Wafer<br>size     | 6"    | m                      | 8"    | 8"    | 12"    | 12"    | 12"        | 12"        |

| Die size<br>(mm²) | 80.7  | 8"                     | 19.2  | 10.7  | 6.7    | 4.2    | 2.4        | 1.4        |

| Dies per<br>wafer | 310   | 46.6<br><del>950</del> | 2550  | 4700  | 12,200 | 18,700 | 26,50<br>0 | 46,50<br>0 |

| 1                 |       | 330                    |       |       |        |        | v          | U          |

### 150X increase in die per wafer

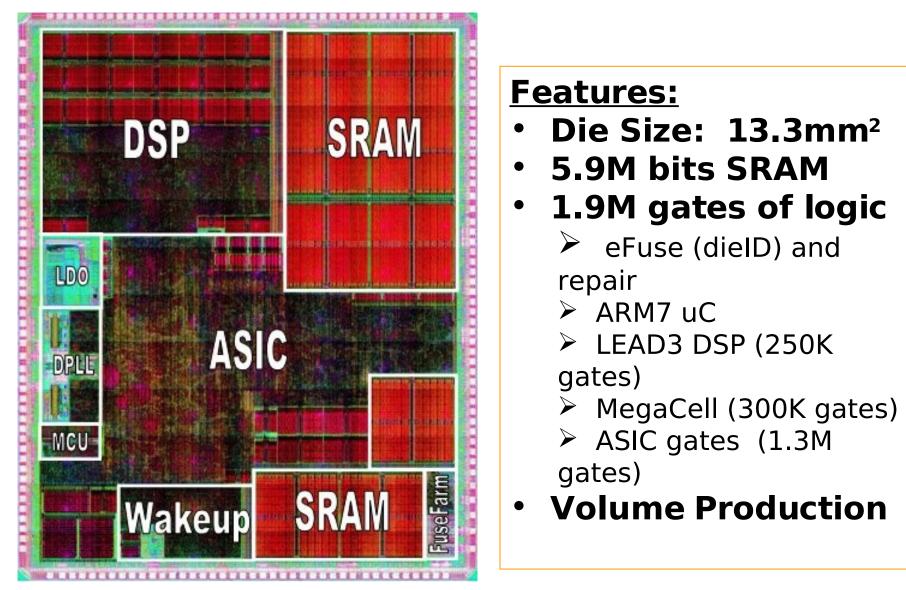

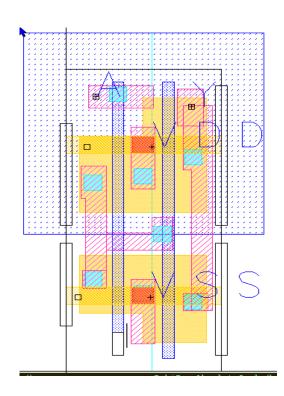

### Typical 65 nm Product: DBB chip

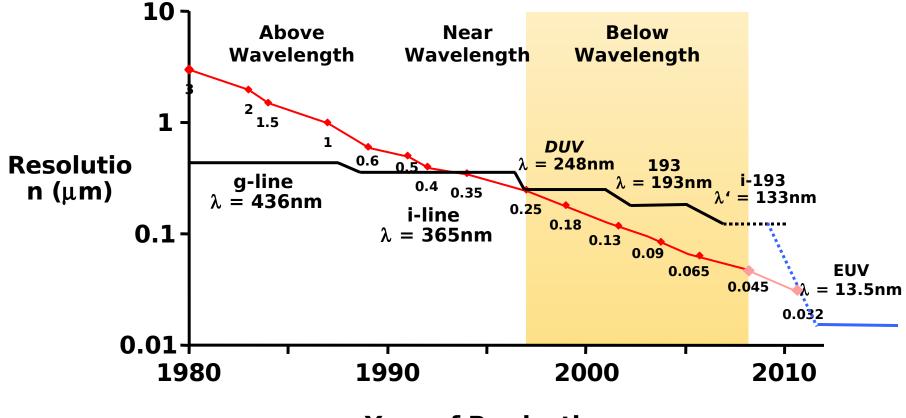

## Lithography

**Year of Production**

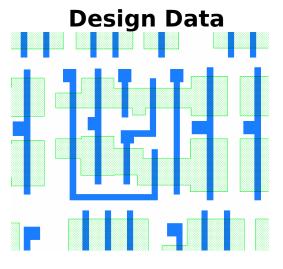

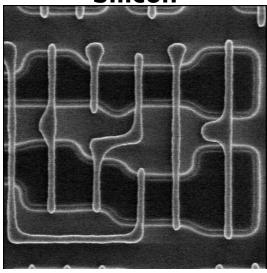

## STRUCTURED LAYOUT (45 nm)

#### Silicon

- Vertical poly gates only

- GHOST Poly

- Poly not required to overlap contact

- Max Xstor width change within ACTIVE

## Si Technology Roadmap Issues/Trends

- Design for Manufacturing Variations

- Analog/RF & MEMS SOC Integration

- Co-Development of Process, Design Techniques and Architecture

- CMOS processes customized to the application

- Relentless focus on power reduction.

## Si TECHNOLOGY ROADMAP FOR UBIQUITOUS COMPUTING AGENDA

- Moore's Law Scaling

- ► Design for Low Power

- SOC Integration of Analog/RF Functions

- Digital Radio Processor

- Integrated MEMS

- Conclusion

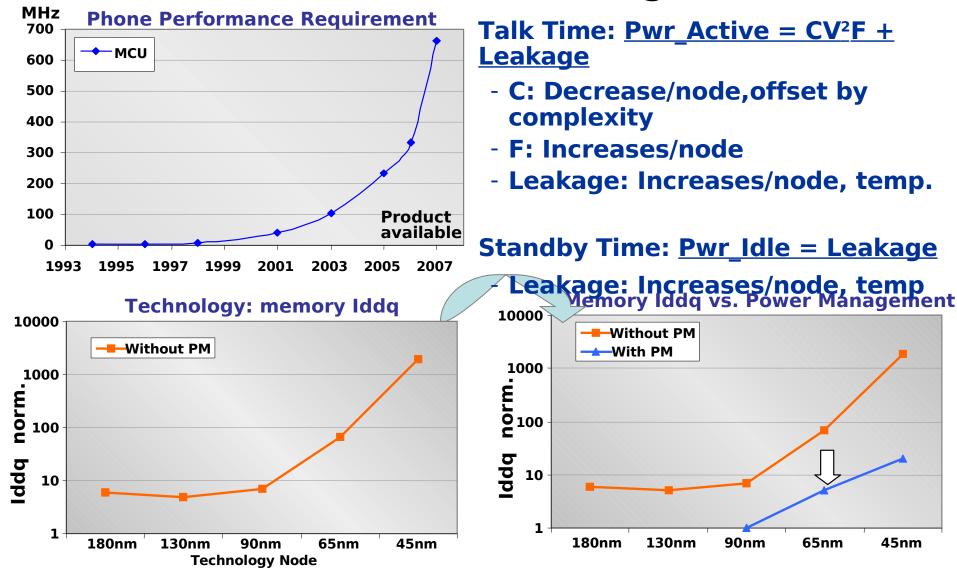

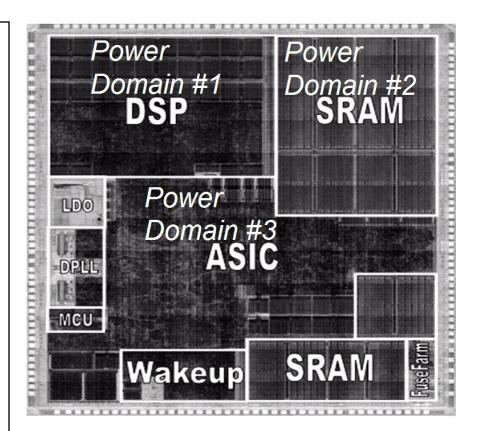

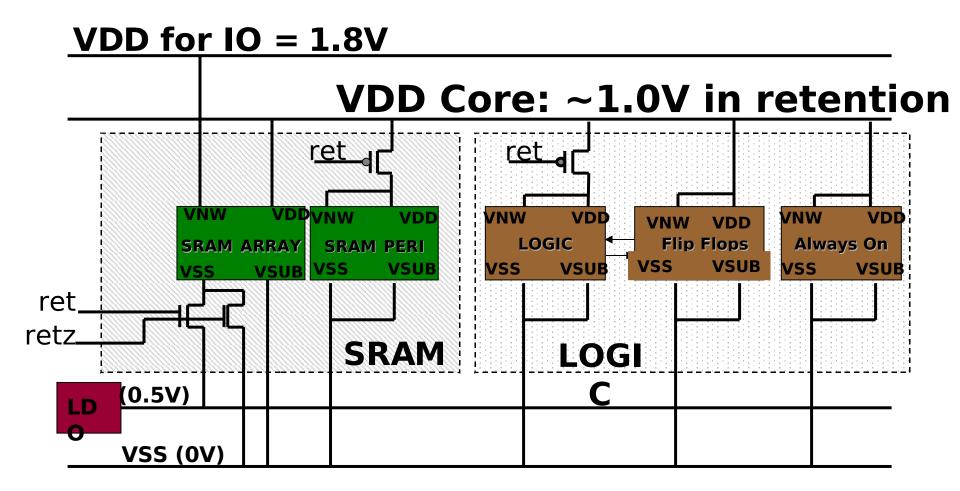

#### Deep Submicron Processes Demand Enhanced Power Management

# **Power Domain Partitioning**

- Main Power

Domains

- DSP

- Data Memory

- Modem Logic

- Others

- Power Mngmt Control

- MCU

- DPLL

- Analog

- 10

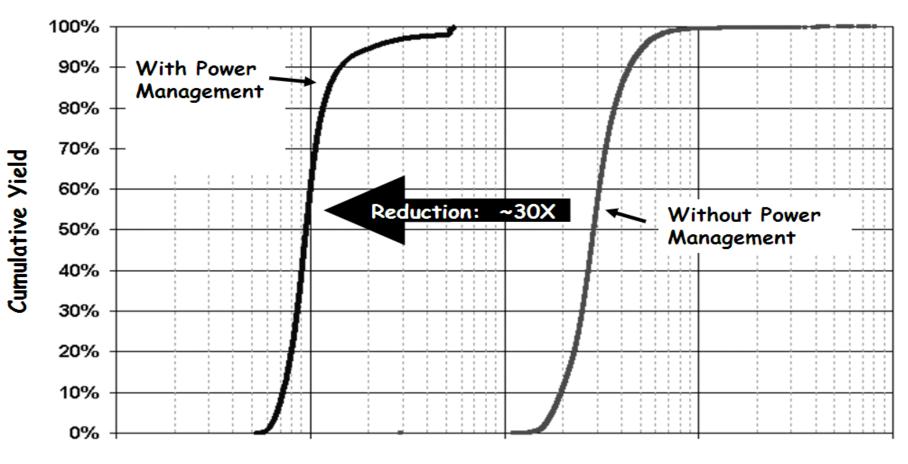

### **Approaches to Power Reduction**

## Silicon Measurements

Iddg at Room Temperature

## Si TECHNOLOGY ROADMAP FOR UBIQUITOUS COMPUTING AGENDA

- Moore's Law Scaling

- Design for Low Power

- SOC Integration of Analog/RF Functions

- Digital Radio Processor

- Integrated MEMS

- Conclusion

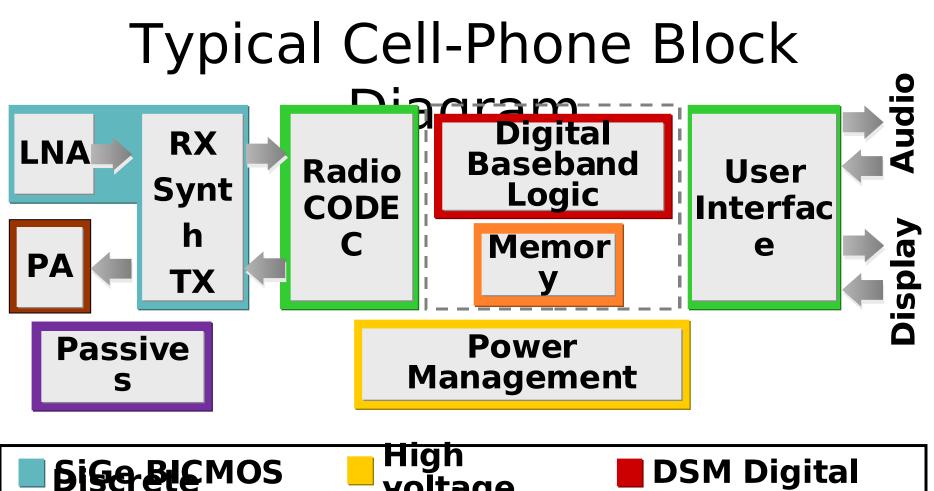

# Why Single-Chip Phone?

- "Integration is like gravity"

- Already happened in harddisk drives, ADSL, etc

- Not a single example of reversal

- "\$20 phones"

- Large untapped market in India and China

- More "real estate" space for advanced features

- Better reliability

- Today, more than half of the total components on a board are analog RF components

- Longer talk time

## What about SiP Integration?

- Monolithic integration of DRAM would result in significant cost increase due to the need for additional mask levels.

- Memory modules are highly reusable so modularity makes sense.

- No yield impact issue due to in-package

| DRAM<br>Chip      | Hi-Perf. Logic<br>Chip | Integrated Logic +<br>eDRAM                       |  |  |  |

|-------------------|------------------------|---------------------------------------------------|--|--|--|

| 50mm <sup>2</sup> | 50mm <sup>2</sup>      | 100mm <sup>2</sup>                                |  |  |  |

| 3LM               | 6LM                    | 6LM + DRAM Mask Levels                            |  |  |  |

| 26 mask levels    | 26 mask levels         | 32 mask levels                                    |  |  |  |

|                   | Cost:<br>mask levels   | Chip Cost:<br>100mm <sup>2</sup> x 32 mask levels |  |  |  |

|                   |                        | 23% Higher Cost                                   |  |  |  |

## Si TECHNOLOGY ROADMAP FOR UBIQUITOUS COMPUTING AGENDA

- Moore's Law Scaling

- Design for Low Power

- SOC Integration of Analog/RF Functions

- ► Digital Radio Processor

- Integrated MEMS

- Conclusion

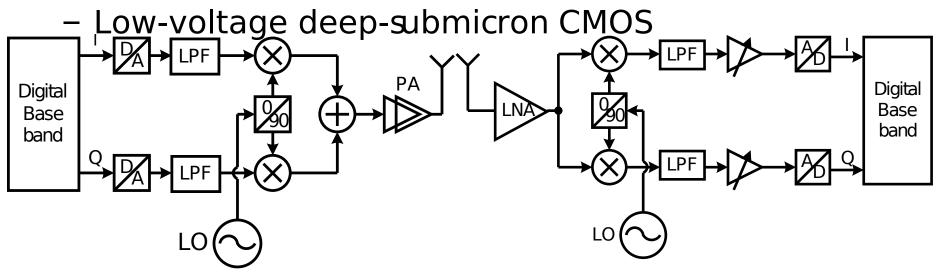

# **Conventional Transceivers**

- RF transmitters in commercial wireless applications are traditionally based on charge-pump PLL's and IQ upconversion mixers

- RF receivers use continuous-time mixing, filtering and amplification

- Design flow and circuit techniques are analog intensive

- Technology incompatible with modern digital processors

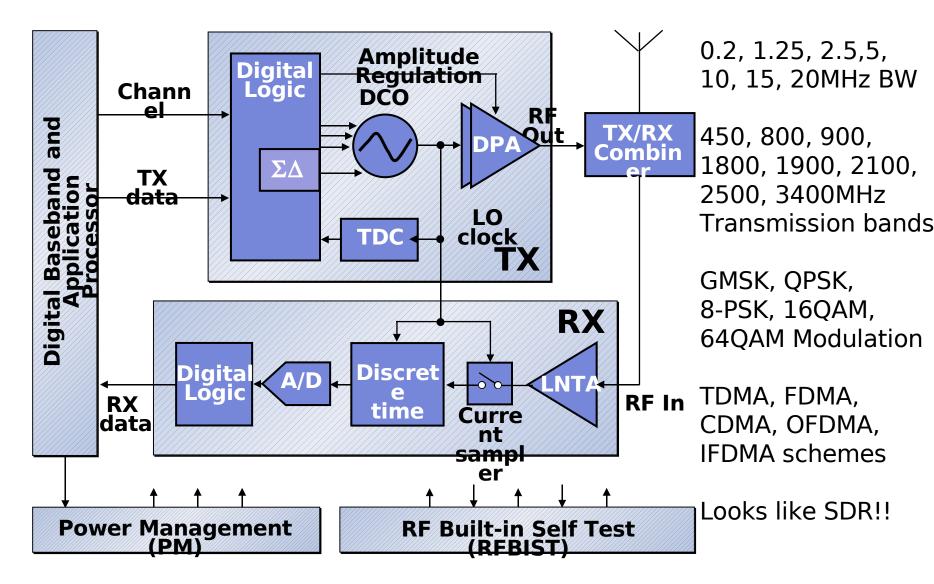

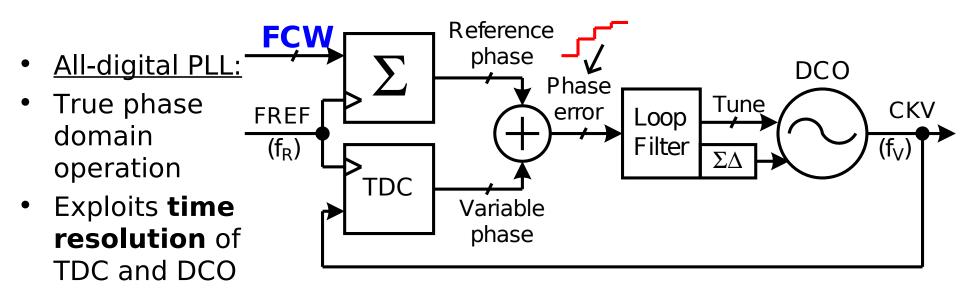

## DRP RF Architecture

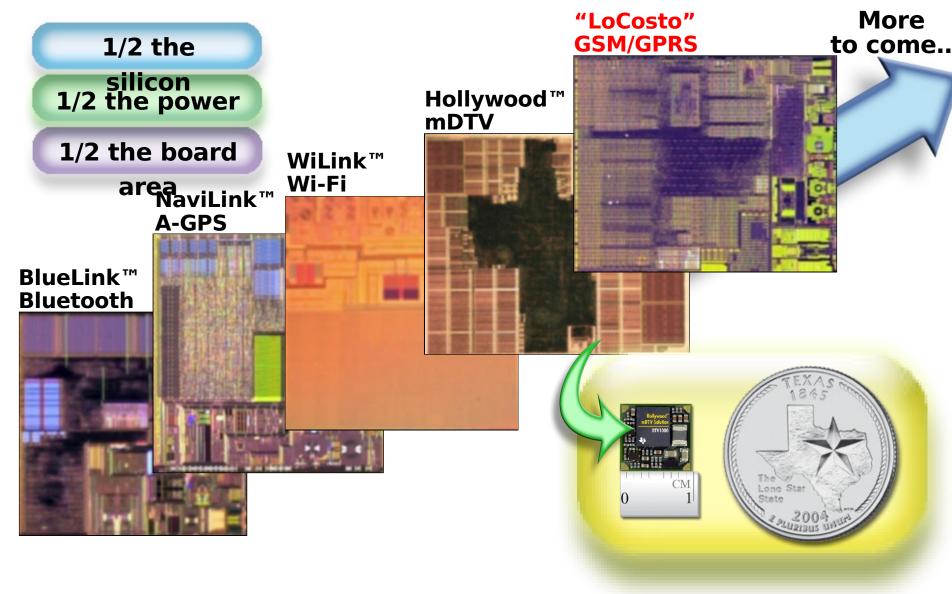

### **DRP/SoC Proven in Many Products**

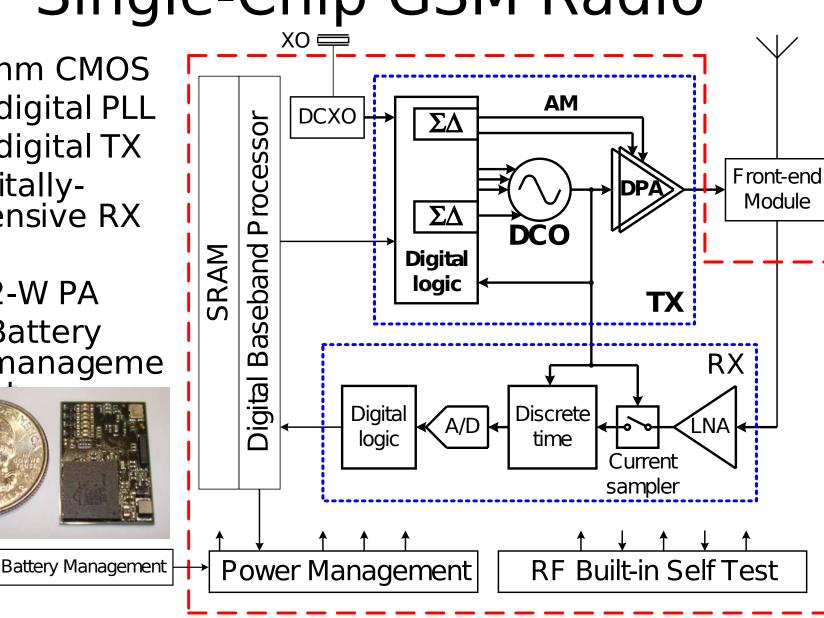

# Single-Chip GSM Radio

- 90 nm CMOS

- **All-digital PLL**

- All-digital TX

- **Digitally**intensive RX

- w/o

- 2-W PA

- Battery manageme

# New Paradigm

In a deep-submicron CMOS process, time-domain resolution of a digital signal edge transition is superior to voltage resolution of an analog signal

#### All-Digital PLL vs. Charge-pump Charge Pump Phase/ Charge-pump Frequency NUL <u>PLL:</u> Detector VCO Loop Filter Suffers from UP FREF PFD reference DOWN $(f_R)$ $(f_V)$ Tuning spurs voltage Tradeoff: m m $\pi$ bandwidth **Frequency Divider** against spur ÷N level

# **Deep-Submicron CMOS Rules**

#### • Exploit:

- Fast switching characteristics of MOS transistors

- Small device geometries and precise device matching

- High density of digital logic: 250 kgates/mm<sup>2</sup> in 90nm CMOS

- High density of SRAM memory: 1 Mbits / mm<sup>2</sup> in 90nm CMOS

#### • Avoid:

- Biasing currents for analog circuits

- Reliance on voltage resolution

- Nonstandard devices not needed for memory and digital logic

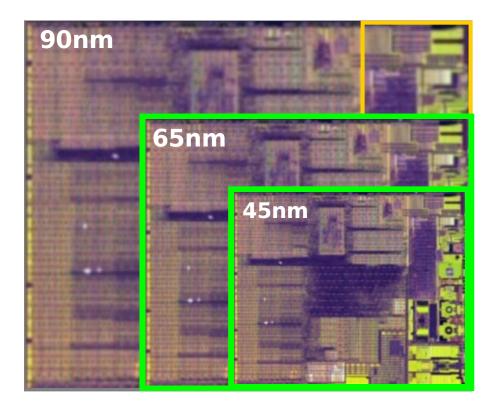

# SoC Drives Cost Reduction

- SoC Integration Includes:

- Digital baseband

- SRAM

- Power management

- Analog

- RF

- Processors & Software

- The DRP technology enables digital implementation of traditional analog RF functions in standard CMOS

- Most advanced process technology used to maximize integration while minimizing cost

- 90nm (shipping)

- 65nm (mature design)

- 45nm and beyond (preliminary)

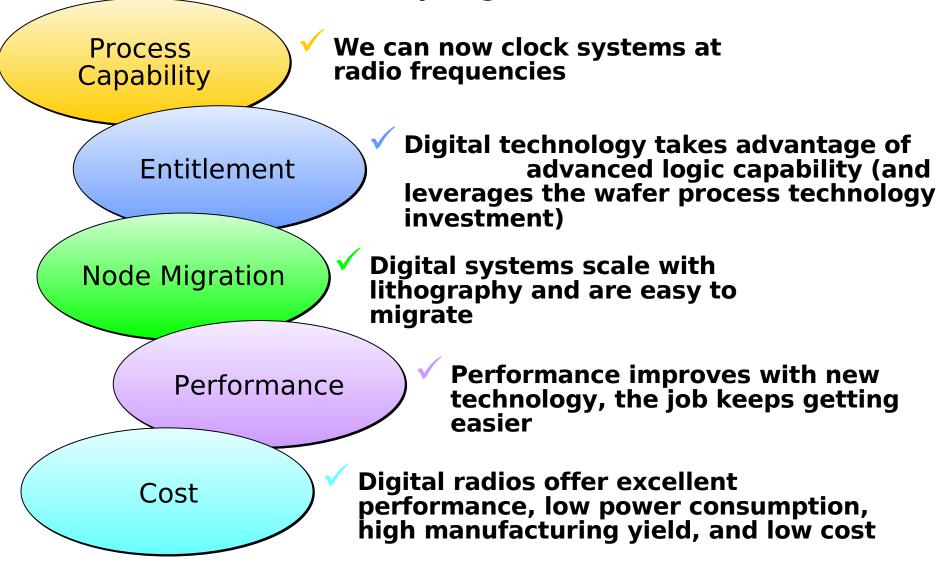

#### Digital Radios Offer Many Benefits Why Digital?

## Si TECHNOLOGY ROADMAP FOR UBIQUITOUS COMPUTING AGENDA

- Moore's Law Scaling

- Design for Low Power

- SOC Integration of Analog/RF Functions

- Digital Radio Processor

- ►Integrated MEMS

- Conclusion

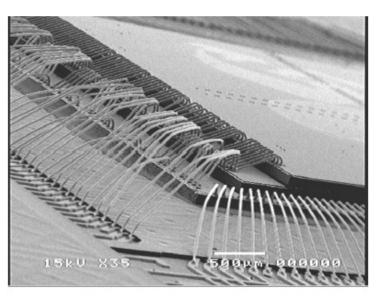

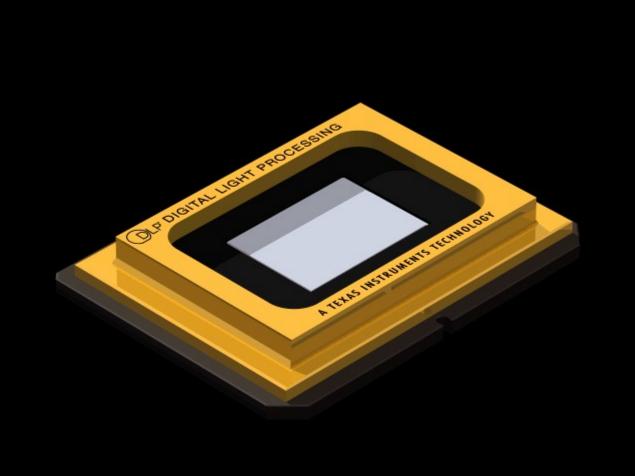

# **MEMS** Integration

- MEMS Integration will also enable products for ubiquitous computing, sensing and perception

- accelerometers

- pressure sensors

- rate gyros

- integrated microphones

- resonators

- RF switches and tuneable capacitors

- optical switches and phase modulators,

- micro-fluidic pumps and valves

- displays

- The Digital Mirror Device (DMD) is an example of integrated MEMS

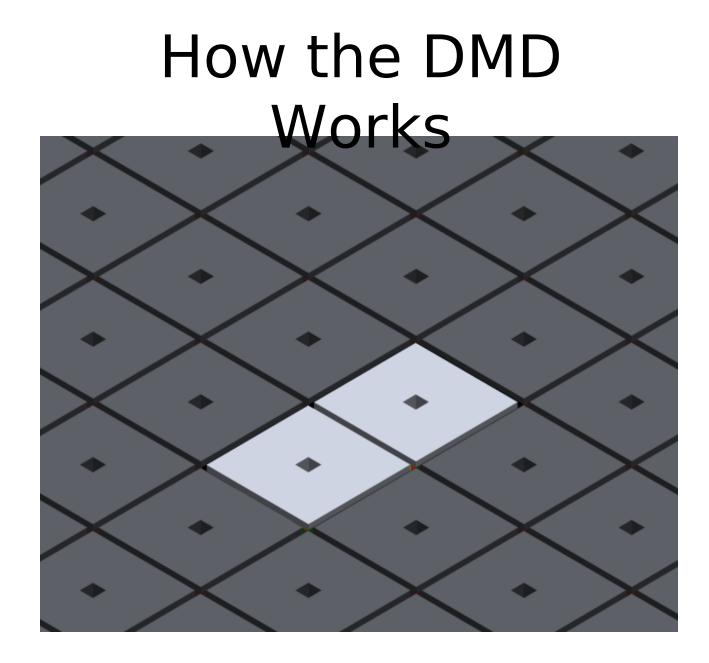

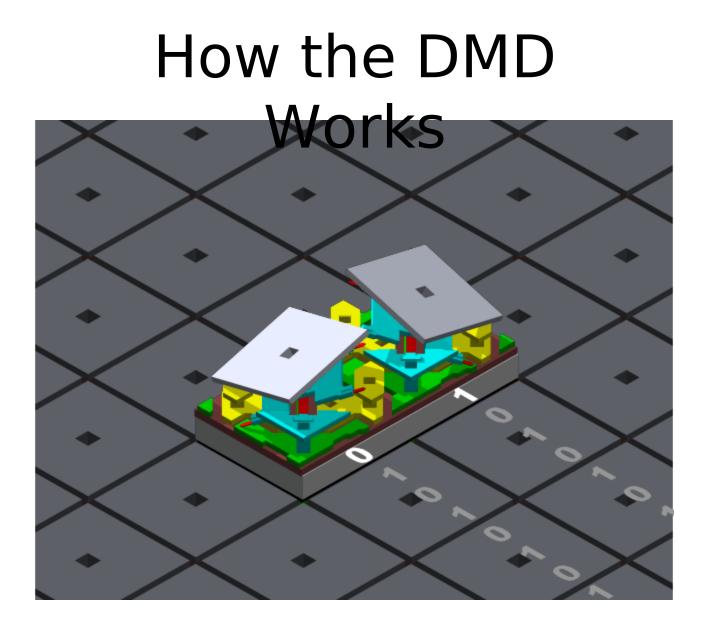

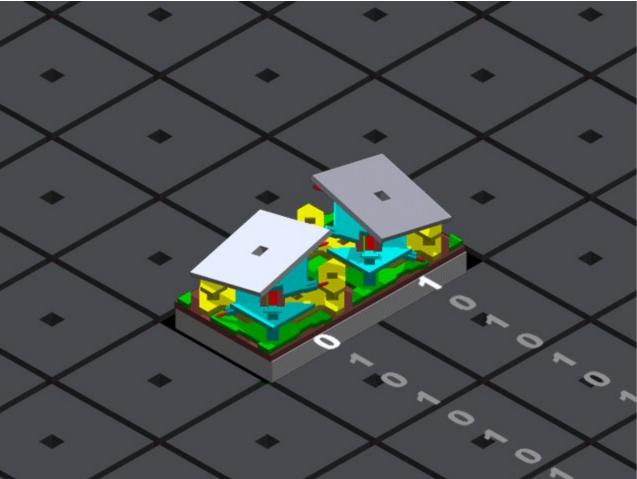

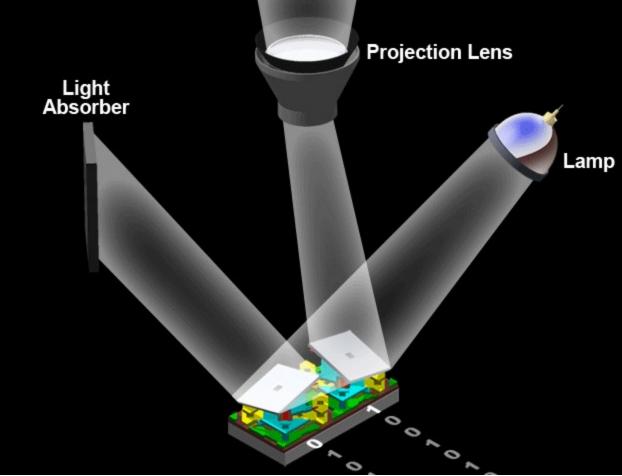

## How the DMD Works

## How the DMD Works

## How the DMD Works

# **MEMS** Integration

#### <u>Today</u>

- HDTV

- Front Projection Products

- Large Screen Movie Theaters

#### **Tomorrow**

- Projection displays for cell phones and PDAs

- 3D imaging for medical

## Si TECHNOLOGY ROADMAP FOR UBIQUITOUS COMPUTING AGENDA

- Moore's Law Scaling

- Design for Low Power

- SOC Integration of Analog Functions

- Digital Radio Processor

- Integrated MEMS

- ►Conclusion

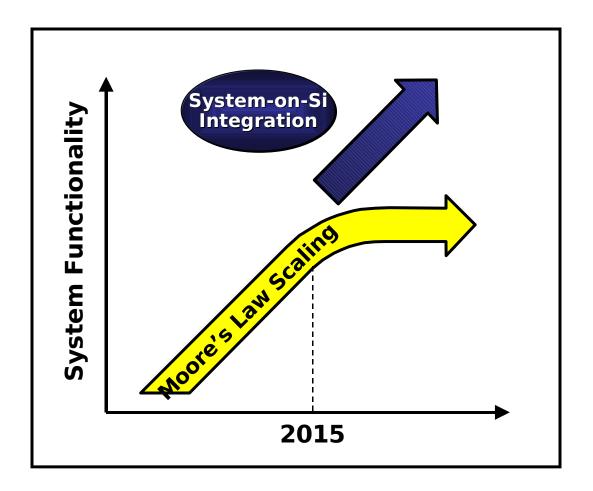

## Technology in the Next Decade

Moore's Law is predicted to stagnate toward the end of the next decade ...

## Technology in the Next Decade

Moore's Law is predicted to stagnate toward the end of the next decade ...

... but SOC Integration has the potential to continue IC cost reduction and to perpetuate growth of products for ubiquitous computing, perception & sensing.

## Systems on Si